Universal Asynchronous Receiver/Transmitter, oft UART genannt, ist ein asynchroner Empfänger/Sender.

Zunächst sollen die Begriffe synchrone und asynchrone Kommunikation eingeführt werden. Synchron bedeutet, dass der Sender nach dem Senden der Daten darauf wartet, dass der Empfänger eine Antwort zurückschickt, bevor er das nächste Datenpaket sendet; asynchron bedeutet, dass der Sender nach dem Senden der Daten darauf wartet, dass der Empfänger sie sendet. Der Teilnehmer sendet eine Antwort zurück und sendet dann die Kommunikationsmethode des nächsten Datenpakets. Mit anderen Worten: synchrone Kommunikation ist ein blockierendes Verfahren, asynchrone Kommunikation ein nicht-blockierendes Verfahren. Unter den gängigen Kommunikationsbusprotokollen gehören I2C und SPI zur synchronen Kommunikation, während UART zur asynchronen Kommunikation gehört. Bei der synchronen Kommunikation müssen die beiden Parteien zunächst eine Synchronisation herstellen, d. h. die Uhren beider Parteien müssen auf die gleiche Frequenz eingestellt werden, und Sender und Empfänger müssen kontinuierlich einen kontinuierlichen Synchronisationsbitstrom senden und empfangen. Beim Senden von Zeichen in der asynchronen Kommunikation kann die sendende Seite jederzeit mit dem Senden von Zeichen beginnen. Daher sind bei der UART-Kommunikation das Datenstartbit und das Stoppbit von wesentlicher Bedeutung.

Hardwareschicht

Der häufig verwendete RS-232-Standard wird hier nicht näher erläutert. Die Hauptsache ist, dass die Tx-Leitung und die Rx-Leitung des entsprechenden Geräts richtig aufeinander abgestimmt sind.

Protokollschicht

In der Protokollschicht wird der Inhalt des Datenpakets festgelegt, das aus einem Startbit, Körperdaten, Prüfbit und Stoppbit besteht. Das Format des Datenpakets muss von beiden kommunizierenden Parteien vereinbart werden, um Daten normal senden und empfangen zu können.

Baudrate: Da es bei der asynchronen Kommunikation kein Taktsignal gibt, müssen sich die beiden Kommunikationsgeräte auf die Baudrate einigen. Üblich sind 4800, 9600, 115200, usw.

Start- und Stoppsignale der Kommunikation: Ein Datenpaket in der seriellen Kommunikation beginnt mit dem Startsignal und endet mit dem Stoppsignal. Das Startsignal des Datenpakets wird durch ein logisches 0-Datenbit dargestellt, während das Stoppsignal des Datenpakets durch 0,5, 1, 1,5 oder 2 logische 1-Datenbits dargestellt werden kann, sofern beide Parteien zustimmen.

Gültige Daten: Unmittelbar nach dem Startbit des Datenpakets folgt der zu übertragende Hauptdateninhalt, auch gültige Daten genannt. Die Länge der gültigen Daten wird häufig auf 8 oder 9 Bits festgelegt.

Datenprüfung: Nach den gültigen Daten folgt eine optionale Datenprüfziffer. Da die Datenkommunikation relativ anfällig für externe Störungen ist, die zu Abweichungen bei den übertragenen Daten führen, kann ein Prüfbit in den Übertragungsprozess eingefügt werden, um dieses Problem zu lösen. Zu den Überprüfungsmethoden gehören ungerade Parität (odd), gerade Parität (even), 0-Parität (space), 1-Parität (mark) und keine Parität (noparity).

Die ungerade Parität erfordert, dass die Anzahl der "1" in den gültigen Daten und Prüfbits eine ungerade Zahl ist. Ein Beispiel: 8 Bit lange gültige Daten sind: 01101001. Zu diesem Zeitpunkt gibt es insgesamt 4 "1 "s. Um den ungeraden Paritätseffekt zu erreichen, wird die Paritätsprüfung Das Paritätsbit ist "1", und die endgültig übertragenen Daten bestehen aus 8 Bits gültiger Daten plus 1 Bit Prüfbit, also insgesamt 9 Bits. Die Anforderungen für gerade Parität und ungerade Parität sind genau umgekehrt. Die Anzahl der "1 "s in den Rahmendaten und Paritätsbits muss eine gerade Zahl sein. Zum Beispiel: Datenrahmen: 11001010. Zu diesem Zeitpunkt beträgt die Anzahl der "1 "s im Datenrahmen 4, ist also gerade. Die Prüfziffer ist "0". 0 Parität bedeutet, dass unabhängig vom Inhalt der gültigen Daten die Prüfziffer immer "0" ist, 1 Parität bedeutet, dass die Prüfziffer immer "1" ist.

Analyse des UART-Funktionsblockdiagramms

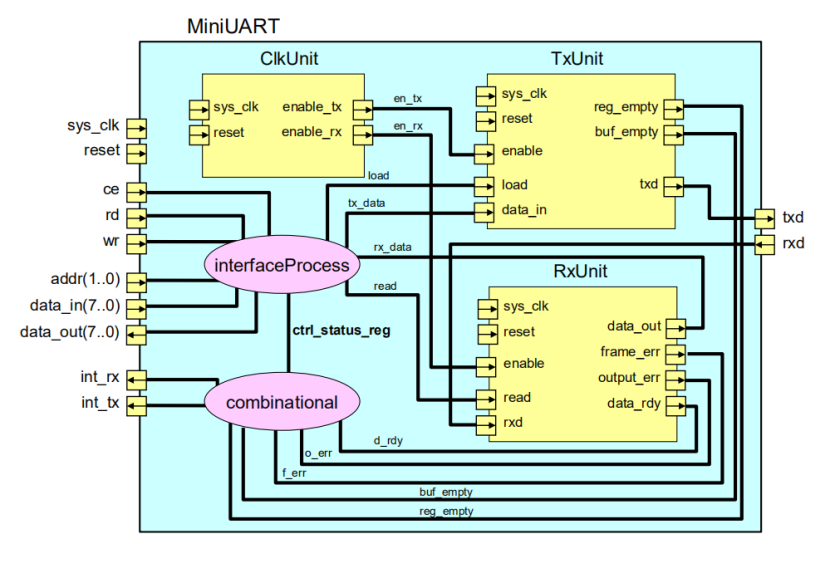

Dieses Bild ist ein Moduldiagramm der UART-Modellierung mit System C, als ich in der Schule war. Für den Schnittstellenteil sind die wichtigsten Tx, Rx Datenausgang, Empfangsschnittstelle und clk liefert das Anfangstaktsignal des Baudratengenerierungsmoduls. Was den Controller-Teil betrifft, so werden hier Logikschaltungen verwendet, um die spezifische Steuerung von Ausgangs-/Empfangsfreigabe, Gerätefreigabe usw. zu implementieren.

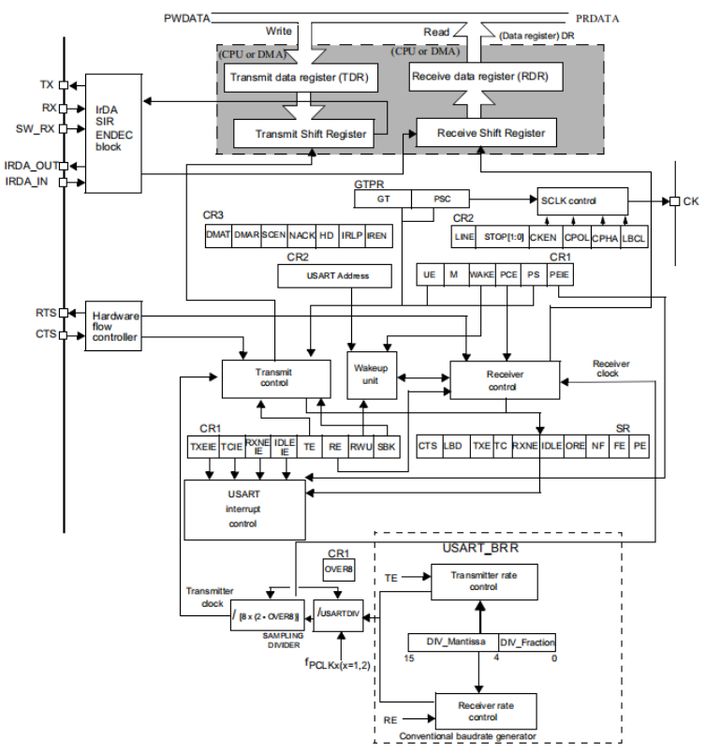

Bei aktuellen Mikrocontrollern ist der Teil der digitalen Schaltung, der die Steuerung übernimmt, gekapselt, so dass man nur noch die entsprechenden Bits des entsprechenden Registers bedienen muss, um den UART zu steuern. Am Beispiel des Chips STM32F411 zeigt die folgende Abbildung das UART-Blockdiagramm:

Modul zur Generierung der Baudrate:

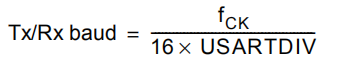

Der Sender und der Empfänger des USART verwenden dieselbe Baudrate, und es gilt folgende Berechnungsformel

Darunter ist fck der USART-Takt, und USARTDIV ist eine vorzeichenlose Festkommazahl, die im Baudratenregister (USART_BRR) gespeichert ist. Die Bits DIV_Mantissa[11:0] definieren den ganzzahligen Teil von USARTDIV, und die Bits DIV_Fraction[3:0] definieren den gebrochenen Teil von USARTDIV.

Zum Beispiel: DIV_Mantissa=24 (0x18), DIV_Fraction=10 (0x0A), dann ist der USART_BRR-Wert 0x18A; dann sind die Dezimalziffern von USARTDIV 10/16=0,625; die Ganzzahlziffern sind 24, und der endgültige Wert von USARTDIV ist 24,625.

Übliche Werte für die Baudrate sind 2400, 9600, 19200 und 115200. Im Folgenden wird anhand eines Beispiels erläutert, wie der Registerwert eingestellt wird, um den Wert der Baudrate zu erhalten. Wir wissen, dass USART1 den APB2-Bustakt verwendet, der bis zu 72 MHz erreichen kann, und die anderen USARTs haben eine maximale Frequenz von 36 MHz. Wir wählen USART1 als Beispiel für die Erläuterung, d.h. fck=72MHz. Um die Baudrate von 115200bps zu erhalten, zu dieser Zeit: 115200=72000000/(16*USARTDIV), die Lösung ist USARTDIV=39.0625, es kann berechnet werden, dass DIV_Fraction=0.0625*16=1=0x01, DIV_Mantissa=39=0x27, das heißt, USART_BRR sollte eingestellt werden Der Wert ist 0x171.

Datenregister:

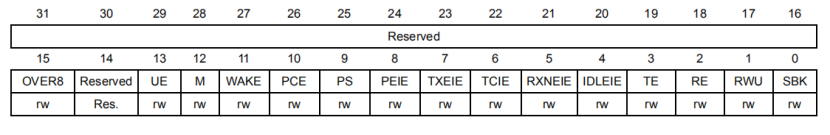

Nur die unteren 9 Bits des UART-Datenregisters (USART_DR) sind gültig, und ob die 9-Bit-Daten gültig sind, hängt von der M-Bit-Einstellung des UART-Steuerregisters 1 (USART_CR1) ab. Wenn das M-Bit 0 ist, bedeutet dies, dass die 8-Bit-Datenwortlänge Ein Wert von 1 steht für eine 9-Bit-Datenwortlänge, und wir verwenden im Allgemeinen eine 8-Bit-Datenwortlänge.

USART_DR enthält gesendete Daten oder empfangene Daten. USART_DR enthält eigentlich zwei Register, ein beschreibbares TDR, das speziell zum Senden verwendet wird, und ein lesbares RDR, das speziell zum Empfangen verwendet wird. Beim Senden werden Daten, die in USART_DR geschrieben werden, automatisch in TDR gespeichert; beim Lesen von Daten in USART_DR werden automatisch RDR-Daten extrahiert.

Sowohl TDR als auch RDR befinden sich zwischen dem Systembus und dem Schieberegister. Die serielle Kommunikation wird Bit für Bit übertragen. Beim Senden wird der TDR-Inhalt an das sendende Schieberegister übertragen, und dann wird jedes Bit der Schieberegisterdaten gesendet. Beim Empfang wird jedes empfangene Bit sequentiell im empfangenden Schieberegister gespeichert und dann an RDR übertragen.

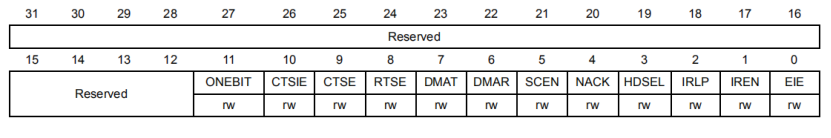

UART unterstützt die DMA-Übertragung, die eine Hochgeschwindigkeitsdatenübertragung (ohne Umweg über die CPU) ermöglicht. Um die DMA-Funktion von UART zu aktivieren, müssen Sie das DMAT-Bit des USART_CR1-Registers auf 1 setzen.

Controller:

UART hat einen Sender, der speziell das Senden steuert, einen Empfänger, der den Empfang steuert, sowie eine Wake-up-Einheit, Interrupt-Steuerung usw. Bevor Sie UART verwenden können, müssen Sie UART aktivieren, indem Sie das UE-Bit des USART_CR1-Registers auf 1 setzen. Das UE-Bit wird verwendet, um den Takt für die serielle Schnittstelle einzuschalten. Die Länge der gesendeten oder empfangenen Daten kann 8 oder 9 Bit betragen, was durch das M-Bit von USARTT_CR1 gesteuert wird.

1) Sender

Wenn das Übertragungsfreigabebit TE des USART_CR1-Registers auf 1 gesetzt ist, wird die Datenübertragung gestartet, und die Daten im Übertragungsschieberegister werden am TX-Pin ausgegeben, wobei das niedrige Bit zuerst und das hohe Bit zuletzt ausgegeben wird.

Eine Zeichenrahmenübertragung besteht aus drei Teilen: Startbit, Datenrahmen und Stoppbit. Das Startbit ist der niedrige Pegel einer Bitperiode, und die Bitperiode ist die Zeit, die jedes Bit beansprucht; der Datenrahmen sind die 8- oder 9-Bit-Daten, die wir senden wollen, und die Daten werden ab dem niedrigsten Bit übertragen; das Stoppbit ist ein bestimmter Zeitabschnitt hohen Pegels.

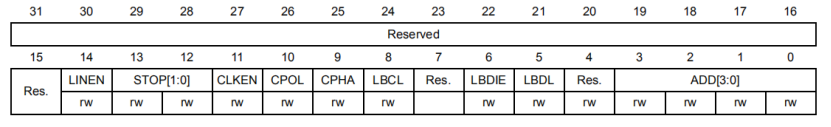

Die Länge der Stoppbits kann über die STOP[1:0]-Bits des UART-Steuerregisters 2 (USART_CR2) gesteuert werden, wobei 0,5, 1, 1,5 und 2 Stoppbits optional sind. Standardmäßig wird 1 Stoppbit verwendet. 2 Stoppbits sind für den normalen USART-Modus, den Einzeldrahtmodus und den Modemmodus verfügbar. 0,5 und 1,5 Stoppbits werden im Smartcard-Modus verwendet.

Wenn das Sendefreigabebit TE auf 1 gesetzt ist, beginnt der Sender mit dem Senden eines Leerrahmens (eine hohe Datenrahmenlänge), und dann können die zu sendenden Daten in das USART_DR-Register geschrieben werden. Nach dem Schreiben der letzten Daten muss gewartet werden, bis das TC-Bit des UART-Statusregisters (USART_SR) auf 1 gesetzt wird, was bedeutet, dass die Datenübertragung abgeschlossen ist. Wenn das TCIE-Bit des USART_CR1-Registers auf 1 gesetzt wird, wird ein Interrupt erzeugt.

Beim Senden von Daten sind mehrere wichtige Flaggen zu beachten:

TE: Sendefreigabe.

TXE: Das Senderegister ist leer, wird verwendet, wenn ein einzelnes Byte gesendet wird.

TC: Übertragung abgeschlossen, wird verwendet, wenn mehrere Bytes an Daten gesendet werden.

TXIE: Freigabe des Übertragungsabschluss-Interrupts.

2) Empfänger

Setzen Sie das RE-Bit des CR1-Registers auf 1, um den USART-Empfang zu aktivieren, so dass der Empfänger mit der Suche nach dem Startbit auf der RX-Leitung beginnt. Nach der Ermittlung des Startbits werden die Daten entsprechend dem Pegelzustand der RX-Leitung im Empfangsschieberegister gespeichert. Nach Abschluss des Empfangs werden die Daten im Empfangs-Schieberegister in den PDR verschoben, und die RXNE-Position des USART_SR-Registers wird geändert. Ein Interrupt kann erzeugt werden, wenn RXNEIE im USART_CR2-Register auf 1 gesetzt ist.

Beim Empfang von Daten sind mehrere wichtige Flaggen zu beachten:

RE: Empfangsfreigabe.

RXNE: Lesedatenregister ist nicht leer.

RXNEIE: Freigabe der Unterbrechung zum Abschluss der Übertragung.

USART_CR1-Register:

USART_CR2-Register:

USART_CR3-Register:

Schlüsselwörter: Modul mit seriellem Anschluss